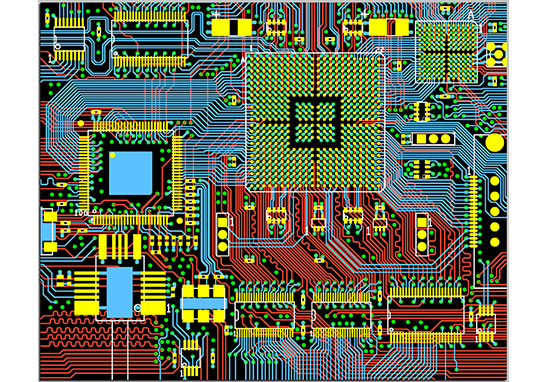

在電路板尺寸固定的情況下���,如果PCB設(shè)計(jì)中需要容納更多的功能,就往往需要提高PCB的走線密度�,但是這樣有可能導(dǎo)致走線的相互干擾增強(qiáng),同時(shí)走線過(guò)細(xì)也使阻抗無(wú)法降低�����,接下來(lái)深圳PCB設(shè)計(jì)公司-宏力捷電子為大家介紹高速高密度PCB設(shè)計(jì)技巧。

高速高密度PCB設(shè)計(jì)技巧

在設(shè)計(jì)高速高密度PCB時(shí)�,串?dāng)_(crosstalk interference)確實(shí)是要特別注意的,因?yàn)樗鼘?duì)時(shí)序(timing)與信號(hào)完整性(signal integrity)有很大的影響����。

高速高密度PCB設(shè)計(jì)注意事項(xiàng):

1. 控制走線特性阻抗的連續(xù)與匹配。

2. 走線間距的大小�。一般常看到的間距為兩倍線寬��?����?梢酝高^(guò)仿真來(lái)知道走線間距對(duì)時(shí)序及信號(hào)完整性的影響���,找出可容忍的最小間距��。不同芯片信號(hào)的結(jié)果可能不同���。

3. 選擇適當(dāng)?shù)亩私臃绞健?/span>

4. 避免上下相鄰兩層的走線方向相同,甚至有走線正好上下重迭在一起���,因?yàn)檫@種串?dāng)_比同層相鄰走線的情形還大�����。

5. 利用盲埋孔(blind/buried via)來(lái)增加走線面積�����。但是PCB板的制作成本會(huì)增加���。

在實(shí)際執(zhí)行時(shí)確實(shí)很難達(dá)到完全平行與等長(zhǎng),不過(guò)還是要盡量做到����。除此以外,可以預(yù)留差分端接和共模端接����,以緩和對(duì)時(shí)序與信號(hào)完整性的影響。

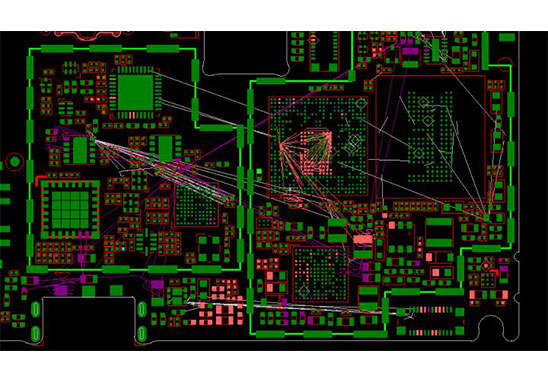

深圳宏力捷PCB設(shè)計(jì)能力

最高信號(hào)設(shè)計(jì)速率:10Gbps CML差分信號(hào)�����;

最高PCB設(shè)計(jì)層數(shù):40層�;

最小線寬:2.4mil;

最小線間距:2.4mil���;

最小BGA PIN 間距:0.4mm���;

最小機(jī)械孔直徑:6mil�����;

最小激光鉆孔直徑:4mil����;

最大PIN數(shù)目:���;63000+

最大元件數(shù)目:3600����;

最多BGA數(shù)目:48+�����。

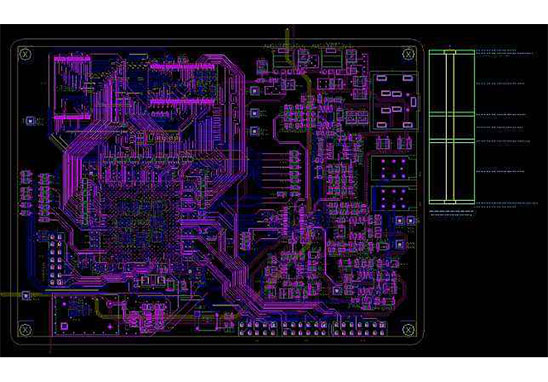

PCB設(shè)計(jì)服務(wù)流程

1. 客戶提供原理圖咨詢PCB設(shè)計(jì)��;

2. 根據(jù)原理圖以及客戶設(shè)計(jì)要求評(píng)估報(bào)價(jià)���;

3. 客戶確認(rèn)報(bào)價(jià)����,簽訂合同,預(yù)付項(xiàng)目定金���;

4. 收到預(yù)付款���,安排工程師設(shè)計(jì)�;

5. 設(shè)計(jì)完成后,提供文件截圖給客戶確認(rèn)����;

6. 客戶確認(rèn)OK,結(jié)清余款�,提供PCB設(shè)計(jì)資料。

深圳宏力捷推薦服務(wù):PCB設(shè)計(jì)打樣 | PCB抄板打樣 | PCB打樣&批量生產(chǎn) | PCBA代工代料