DC-DC電路的PCB設(shè)計(jì)比LDO會復(fù)雜很多,噪聲也更大��,布局和layout要求更高���,layout的好壞直接影響DC-DC的性能����,所以了解DC-DC的layout至關(guān)重要�����。

一��、Bad layout

- EMI����,DC-DC的SW管腳上面會有較高的dv/dt, 比較高的dv/dt會引起比較大的EMI干擾�;

- 地線噪聲,地走線不好�,會在地線上面會產(chǎn)生比較大的開關(guān)噪聲��,而這些噪聲會影響到其它部分的電路���;

- 布線上產(chǎn)生電壓降,走線太長�,會使走線上產(chǎn)生壓降,而降低整個(gè)DC-DC的效率����;

二、一般原則

- 開關(guān)大電流回路盡量短��;

- 信號地和大電流地(功率地)單獨(dú)走線�,并在芯片GND處單點(diǎn)連接;

1. 開關(guān)回路短

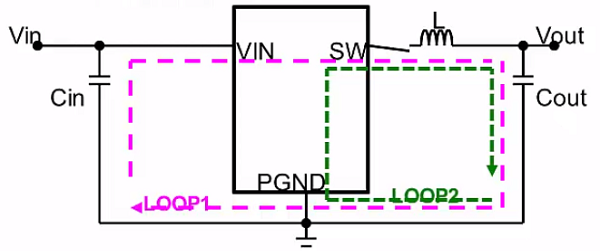

下圖中紅色LOOP1為DC-DC高邊管導(dǎo)通�,低邊管關(guān)閉時(shí)的電流流向;綠色LOOP2的為高邊管關(guān)閉�����,低邊管開啟時(shí)的電流流向��;

為使這兩個(gè)回路盡量小����,引入更少的干擾,需要遵從如下幾點(diǎn)原則:

- 電感盡量靠近SW管腳�;

- 輸入電容盡量靠近VIN管腳;

- 輸入輸出電容的地盡量靠近PGND腳��;

- 使用鋪銅的方式走線�����;

為什么要這么做�?

- 走線過細(xì)過長會增大阻抗,大電流在此大阻抗上會產(chǎn)生比較高的紋波電壓����;

- 走線過細(xì)過長會增大寄生電感,此電感上耦合開關(guān)噪聲�����,影響DC-DC穩(wěn)定性����,造成EMI問題;

- 寄生電容和阻抗會增大開關(guān)損耗和導(dǎo)通損耗���,影響DC-DC效率��;

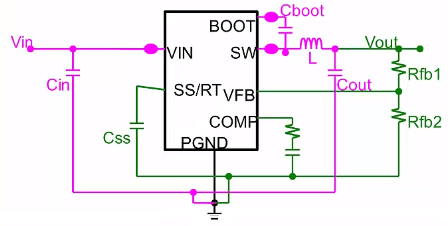

2. 單點(diǎn)接地

單點(diǎn)接地���,指的是信號地和功率地進(jìn)行單點(diǎn)接地���,功率地上會有比較大的開關(guān)噪聲,所以需要盡量避免對敏感小信號造成干擾��,如FB反饋管腳��。

- 大電流地:L��,Cin���,Cout����,Cboot連接到大電流地的網(wǎng)絡(luò)�;

- 小電流地:Css,Rfb1�����,Rfb2單獨(dú)連接到信號地的網(wǎng)絡(luò)�����;

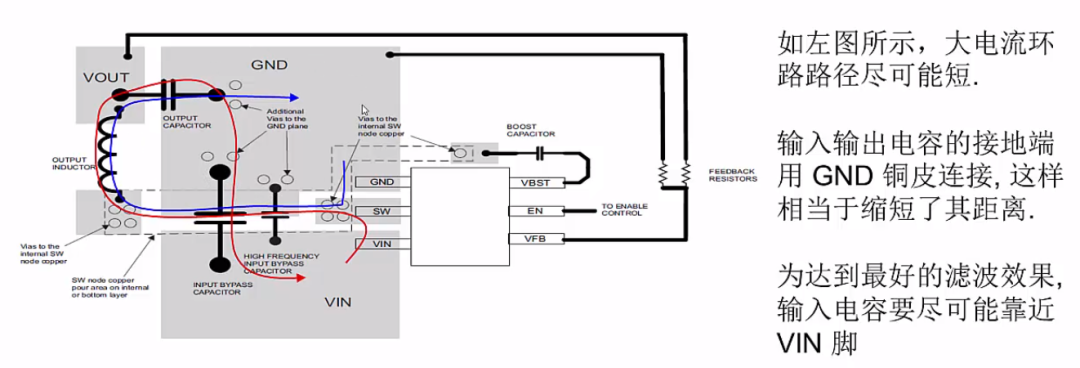

下圖是TI的一個(gè)開發(fā)板的layout����,紅色為上管開時(shí)的電流路徑,藍(lán)色為下管開時(shí)的電流路徑�����;如下的layout有如下比較好的優(yōu)點(diǎn):

- 輸入輸出電容的GND用銅皮進(jìn)行連接���,擺件時(shí)�����,兩者的地盡量放一起�;

- DC-DC Ton和Toff時(shí)的電流路徑都很短���;

- 右邊小信號是單點(diǎn)接地���,距離比較遠(yuǎn),免受左邊大電流開關(guān)噪聲的影響�����;

TI某開發(fā)板的DC-DC PCB layout

三、實(shí)例

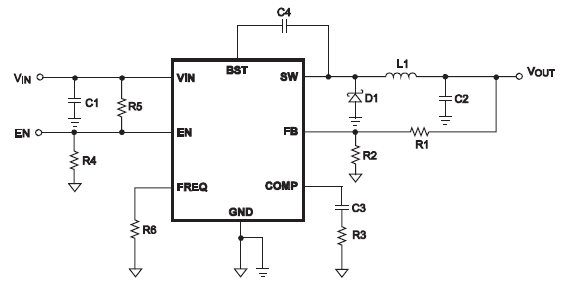

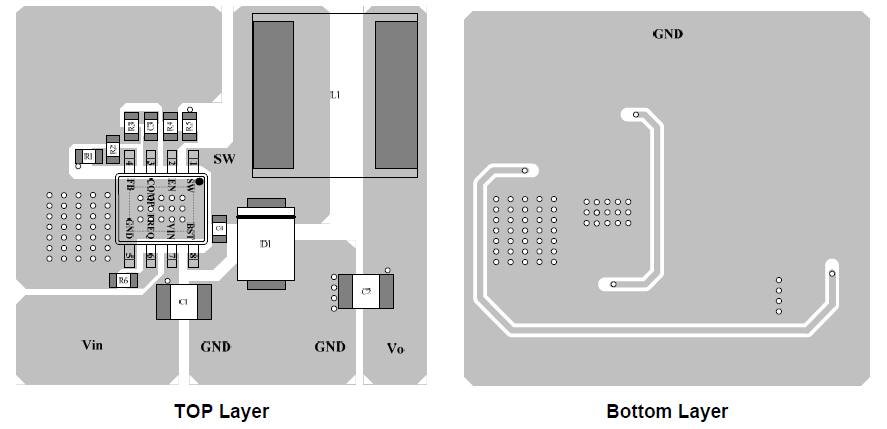

如下給出一個(gè)典型DC-DC BUCK電路的layout����,SPEC中給出如下幾點(diǎn):

- 輸入電容,高邊MOS管�,和續(xù)流二極管形成的開關(guān)回路盡可能小和短;

- 輸入電容盡可能靠近Vin Pin腳�;

- 確保所有反饋連接短而直接,反饋電阻和補(bǔ)償元件盡可能靠近芯片����;

- SW遠(yuǎn)離敏感信號,如FB���;

- 將VIN�����、SW��,特別是GND分別連接到一個(gè)大的銅區(qū)��,以冷卻芯片�����,提高熱性能和長期可靠性�����;

DC-DC BUCK典型電路

layout指導(dǎo)

四���、總結(jié)

DC-DC電路的layout至關(guān)重要,直接影響到DC-DC的工作穩(wěn)定性和性能�����,一般DC-DC芯片的SPEC都會給出layout指導(dǎo)�,可參考進(jìn)行設(shè)計(jì)。

深圳宏力捷電子是一家專業(yè)從事電子產(chǎn)品電路板設(shè)計(jì)(layout布線設(shè)計(jì))的PCB設(shè)計(jì)公司�,主要承接多層、高密度的PCB設(shè)計(jì)畫板及電路板設(shè)計(jì)打樣業(yè)務(wù)���。擁有平均超過10年工作經(jīng)驗(yàn)的PCB設(shè)計(jì)團(tuán)隊(duì)��,能熟練運(yùn)用市場主流PCB設(shè)計(jì)軟件����,專業(yè)高效溝通保證PCB設(shè)計(jì)進(jìn)度,助您早一步搶占市場先機(jī)����!

深圳宏力捷推薦服務(wù):PCB設(shè)計(jì)打樣 | PCB抄板打樣 | PCB打樣&批量生產(chǎn) | PCBA代工代料